- Solutions

- Products

- Resources

- Company

Investor Relations

Investor RelationsFinancial Information

- Careers

Ceva Press Releases

Latest Company Announcements

Ceva’s 20 Billion Device Milestone Paves the Way for a New Era in Smart Edge Innovation

Learn More

Ceva to Participate in Upcoming Investor Conferences and Industry Events

Ceva, Inc. Announces Fourth Quarter and Full Year 2025 Financial Results

Ceva, Inc. Announces Fourth Quarter and Full Year 2025 Financial Results

Ceva-XC21 Named “Best IP/Processor of the Year” at EE Awards Asia

Ceva, Inc. Announces Third Quarter 2025 Financial Results

Ceva, Inc. Announces Second Quarter 2025 Financial Results

Ceva, Inc. To Participate at Upcoming Investor Events

Ceva and Sharp Collaborate on “Beyond 5G” IoT Terminals

Ceva, Inc. Announces Fourth Quarter and Full Year 2024 Financial Results

Ceva, Inc. Appoints Amir Faintuch to its Board of Directors

Ceva Embedded AI NPUs Gain Traction in AIoT and MCU Markets

Ceva Expands Embedded AI NPU Ecosystem with New Partnerships

Ceva Inc. to Join Upcoming Investor Events

Ceva Expands Share Repurchase Program

Ceva, Inc. Announces Third Quarter 2024 Financial Results

PiMCHIP Deploys Ceva Sensor Hub DSP in New Edge AI SoC

Ceva and Edge Impulse Team Up to Accelerate Edge AI Dev

Ceva, Inc. Announces Second Quarter 2024 Financial Results

Ceva Bluetooth and 802.15.4 IPs Power Wireless IoT MCUs

STMicro Uses Ceva Cellular IoT Platform in NB-IoT Module

Ceva Joins Arm to Accelerate 5G SoC Dev for Infra & Satellites

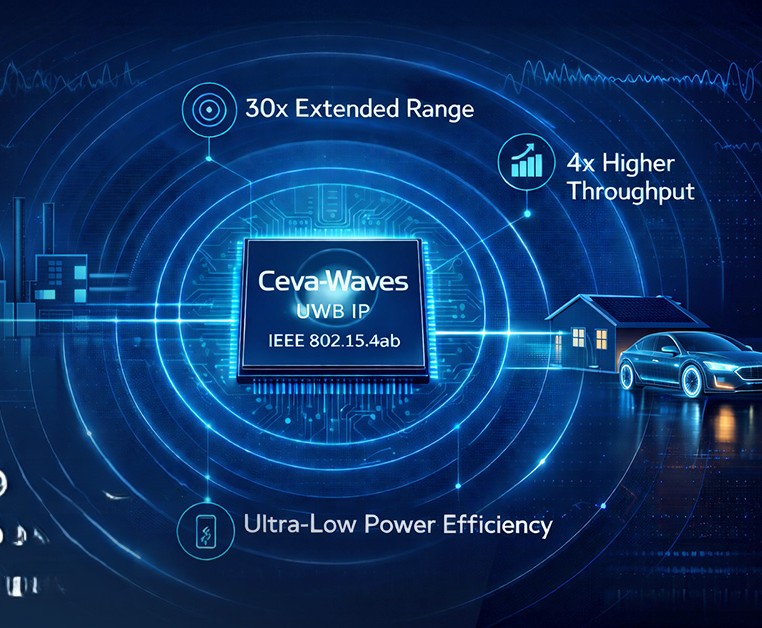

Ceva Launches Low Power UWB IP for Accurate IoT Ranging

Ceva Reports Q4 and Full Year 2023 Financial Results

SKAIChips Adopts Ceva Bluetooth for Shelf Labels

Ceva and boAt Partner to Enhance Wireless Audio Experience

Ceva, Inc. Participates at Investor Events

Ceva, Inc. Announces Expansion of Existing Share Repurchase Program

CEVA, Inc. Announces Third Quarter 2023 Financial Results

CEVA, Inc. to Host Investor Day on December 6, 2023

CEVA, Inc. Appoints Iri Trashanski as Chief Strategy Officer

Cadence to Acquire Intrinsix Corporation from CEVA

CEVA, Inc. Announces Second Quarter 2023 Financial Results

Ceva Boosts GenAI with Enhanced NeuPro-M NPU IP Family

CEVA Wi-Fi 6 IP Powers ESWIN ECR6600 Smart Connectivity IC

Ceva Reports Q4 and Full Year 2022 Financial Results

CEVA, Inc. to Present at the 25th Annual Needham Growth Conference

CEVA, Inc. Names Gweltaz Toquet as Chief Commercial Officer

Novatek Uses Ceva DSP in Multi-Sensor IP Camera SoC

CEVA Joins Intel Pathfinder for RISC-V Program

CEVA, Inc. Announces CEO Transition Plan

CEVA, Inc. Announces Third Quarter 2022 Financial Results

CEVA, Inc. Announces Second Quarter 2022 Financial Results

CEVA Celebrates 15 Billionth CEVA-powered Chip Shipped

CEVA, Inc. to Participate in the 34th Annual ROTH Conference

CEVA, Inc. Announces Fourth Quarter 2021 Financial Results

CEVA, Inc. to Present at Upcoming Virtual Investor Conferences

CEVA, Inc. Announces Third Quarter 2021 Financial Results

CEVA, Inc. Announces Second Quarter 2021 Financial Results

Nations’ Latest BLE 5 IC Powered By CEVA Bluetooth® Low Energy IP

CEVA, Inc. Announces Fourth Quarter and Year End 2020 Financial Results

CEVA and DARPA Establish Partnership for Technology Innovation

Retune DSP’s Wake Word Engine Now Available for CEVA Audio/Voice DSPs

Ceva DSP to Power Renesas’ Next-Gen Automotive SoC

CEVA, Inc. to Present at Upcoming Virtual Investor Conferences

CEVA, Inc. Announces Third Quarter 2020 Financial Results

CEVA, Inc. Announces Second Quarter 2020 Financial Results

Picocom License CEVA DSP for 5G New Radio Infrastructure SoC

Bragi and CEVA Collaborate to Redefine Hearable Devices

CEVA Unveils World’s Most Powerful DSP Architecture

CEVA, Inc. Announces Fourth Quarter and Year End 2019 Financial Results

CEVA, Inc. to Present at Upcoming Investor Conferences

CEVA, Inc. Announces Third Quarter 2019 Financial Results

CEVA Appoints Bernadette Andrietti to its Board of Directors

CEVA, Inc. to Present at Upcoming Investor Conferences

CEVA, Inc. Announces Second Quarter 2019 Financial Results

Nurlink Launches NB-IoT and GNSS SoC Powered by CEVA-Dragonfly NB2 IP

Autotalks and CEVA Collaborate on World’s First Global V2X Solution

HILLCREST LABS AND LG RENEW LICENSE FOR SMART TV TECHNOLOGY

CEVA, Inc. Announces Fourth Quarter and Year End 2018 Financial Results

CEVA Locates More Success with Bluetooth® 5.1 IP

CEVA Opens New Research and Development Center in Bristol, U.K.

Bestechnic Picks Ceva Bluetooth 5 IP for Audio Platforms

CEVA, Inc. to Host First Investor and Analyst Day

CEVA, Inc. Announces Third Quarter 2018 Financial Results

SigmaStar Uses Ceva Vision AI Platform in Smart Camera SoC

CEVA Adds ONNX Support to CDNN Neural Network Compiler

CEVA, Inc. to Present at Upcoming Investor Conferences

CEVA, Inc. Announces Second Quarter 2018 Financial Results

CEVA First to Deliver Bluetooth® 5 Dual Mode IP

CEVA and Nokia Collaborate for 4.9G and 5G Technologies

Ceragon License CEVA DSPs for Full 5G Wireless Backhaul

CEVA Extends its IP Platforms for Bluetooth and Wi-Fi with RISC-V

CEVA Announces Industry’s First 802.11ax Wi-Fi IPs

CEVA, Inc. to Present at Upcoming Investor Conferences

CEVA, Inc. Announces Third Quarter 2017 Financial Results

CEVA and LG Electronics Partner for Smart 3D Camera Solution

CEVA Named on the FORTUNE 2017 “100 Fastest-Growing Companies®” List

Nextchip License CEVA Imaging and Vision Platform for ADAS Vision System

CEVA, Inc. Announces Second Quarter 2017 Financial Results

SRT Group License CEVA Signal Processing IP

CEVA Leads the Bluetooth® 5 IP Wave

CEVA, Inc. Announces Third Quarter 2016 Financial Results

Espressif Licenses and Deploys CEVA Bluetooth in ESP32 IoT Chip

CEVA, Inc. to Present at Upcoming Financial Conferences

CEVA, Inc. Announces Second Quarter 2016 Financial Results

ITRI Selects CEVA-XC DSP for 4G Small Cell Base Stations

LG Electronics Selects CEVA Imaging and Vision DSP for Mobile Devices

CEVA, Inc. Announces Fourth Quarter and 2015 Financial Results

CEVA, Inc. to Present at Upcoming Conferences November 4, 2015

CEVA, Inc. Announces Third Quarter 2015 Financial Results

CEVA, Inc. to Present at Upcoming Conferences August 6, 2015

Ceva’s 1GHz DSP Core Boosts Comms and Multimedia SoCs

CEVA DSP Powers Samsung’s First Generation LTE Modem

ParthusCeva Changes Name to CEVA, Inc.

Ceva and Parthus Complete Merger and Launch Operations

Parthus Technologies to Acquire Chicory Systems

Parthus Expands Executive Team with Key Appointments

Parthus Unveils Bluetooth™ Demos Including MP3 File Sharing

Parthus MediaStream DSP Selected by NVIDIA

Parthus appoints Chief Operating Officer Kevin Fielding to Board

Get in touch

Reach out to learn how can Ceva help drive your next Smart Edge design